## **JNPV 2016**

## Determination of the damage depth profile after diamond wire sawing of silicon wafers using minority carrier lifetime measurements

R. Souidi<sup>a,b</sup>, A. Chabli<sup>a,b</sup>, N. Enjalbert<sup>a,b</sup>, F. Coustier<sup>a,b</sup>, F. Bertin<sup>c,d</sup>

<sup>a</sup> Univ. Grenoble Alpes, INES, F-73375 Le Bourget du Lac, France

<sup>b</sup> CEA, LITEN, Department of Solar Technologies, F-73375 Le Bourget du Lac, France

<sup>c</sup> Univ. Grenoble Alpes, F-38000 Grenoble, France

<sup>d</sup> CEA, LETI, MINATEC Campus, F-38054, Grenoble, France

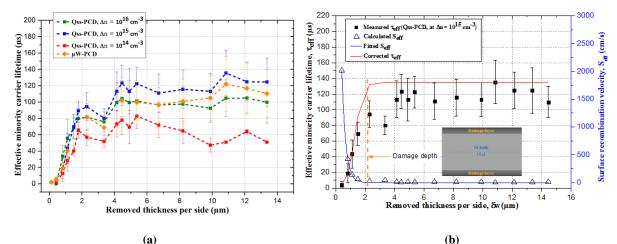

*The* diamond wire sawing (DWS) is an emerging technology for wafering semiconductor ingots, which promises many advantages over the existing dominant technology of slurry cutting. But wafering is known to leave regions of damage on each surface of the wafer, typically several micrometers deep, in the form of dislocations that remain close to the surface, phase transformations of Si, micro-cracks and lattice distortions. Because the surface damage must be removed prior to solar cell fabrication, and there is a tendency to go to lower thicknesses, it is important that the depth of damage be a controlled parameter. There are a number of approaches for measuring the damage introduced by the wafering process, such as XRD, TEM, and beveled section polishing followed by defect etching [1]. All these techniques are time consuming and only provide a qualitative and local information on depth of damage that can greatly vary over the wafer cutting by DWS. Thus, it is essential to develop fast and simple techniques to determine spatially-averaged depth of damage introduced by wafer sawing. The present work will report on a new approach for measuring an average damage depth over a large area using minority carrier lifetime measurement. Although the proposed method is simple, its experimental implementation requires two essential tasks: (i) a chemical etchant that can remove thin layers in a highly controlled manner and (ii) a reproducible lifetime measurement using Qss-PCD technique for instance. Then the surface recombination velocity is extracted from the lifetime measurements on wafers for different removed thicknesses from the surface based on a simple model proposed by Sopori and al [3] as shown in Figure 1. This method can be easily adapted in a solar cell facility that has a lifetime measurement system

**Figure 1** – (a) Plots of measured lifetime as a function of removed thickness per side for  $\mu$ W-PCD and Qss-PCD measurement techniques, (b) the minority carrier lifetime ( $\tau_{eff}$ ) and the surface recombination velocity ( $S_{eff}$ ) fits as a function of the removed thickness (for one injection level of Qss-PCD plots,  $\Delta n = 10^{15} \text{ cm}^{-3}$ ),  $S_{eff}$  is fitted using Sopori model [2]

[1] W. Lu and al, International Journal of Machining and Machinability of Materials 2, vol. 2, no. 1, pp. 125–142, 2007

[2] B. Sopori and al, in 2015 IEEE 42nd Photovoltaic Specialist Conference, PVSC 2015, 2015

This work has received support from the French National Program «Investment for the future» in the frame of the INES2 project bearing the reference ANR-10-ITE-0003